# Fact Sheet MPW Run #4

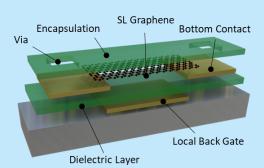

The fourth MPW run is mainly intended towards electronics but can also include sensor devices (e.g. Hall sensor, but via opening on graphene is not in the scope of this run) and will be provided by AMO GmbH. The design of the device can be adjusted within the specifications. The offered device structure is a GFET (Fig. 1) consisting of the following fabrication steps:

- Local Back gate (Au or Pd)

- Dielectric deposition & vias opening

- Bottom contacts fabrication (as local BG)

- Wafer-scale graphene transfer & patterning

- Encapsulation & vias opening (not on top of graphene)

- Optional: Au Bondpads

The summary of the key parameters for a device with local back gate is shown in the table below.

| Parameter                  |                                            | Value        |

|----------------------------|--------------------------------------------|--------------|

| Graphene Mobility          |                                            | >1000 cm²/Vs |

| Avg. Sheet<br>Resistance   | n=-5 x 10 <sup>12</sup> cm <sup>-2</sup> : | ~1 kΩ        |

| Avg. Contact<br>Resistance | n=-5 x 10 <sup>12</sup> cm <sup>-2</sup> : | ~1 kΩ μm     |

| Minimum work               | >80 %                                      |              |

| Dirac point                |                                            | -10 V +10 V  |

| Safe gate-source           | ± 20 V                                     |              |

## **Timeline**

- During the application phase, interested clients can contact us via the contact form and receive further information about the run in a first meeting.

- Final Layout Submission and PO must be received by 22 June 2026.

- The chips are expected to be delivered in November 2026.

Figure 1 Scheme with the different layers of the final GFET structure.

## **Specifications**

#### **Substrate**

- Material: Silicon/SiO<sub>2</sub> (90nm)

- o Si Resistivity 1-10 Ohm-cm

- O Thickness 675+/-25μm

- Basic die size: 1 x 1 cm<sup>2</sup>

#### Resolution

General design rule: 10 µm for in-layer critical dimension and over-layer alignment

### **Layer Thicknesses**

|   | <u> </u>              |                         |            |

|---|-----------------------|-------------------------|------------|

| # | Rigid Substrate       | Si/SiO <sub>2</sub>     | 90 nm      |

| 1 | Back Gate Contact     | Ti/Pd or<br>Ti/Au       | 5nm /40nm  |

| 2 | Dielectric Layer      | $Al_2O_3$               | 40 nm      |

| 3 | <b>Bottom Contact</b> | as layer 1              | 5nm /40 nm |

| 4 | Graphene              | Single layer, CVD on Cu |            |

| 5 | Encapsulation         | $Al_2O_3$               | 40 nm      |

| 6 | Bondpads              | Au                      | 300 nm     |

#### Characterization

- Raman characterization

- Electrical measurement for asfabricated reference devices

- General optical inspection of your devices

### Costs

- 3600,-€ set price for 8 dies with identical design (1x1 cm²)

- Each die more with identical design costs 450,-€ in addition

- 50% discount is possible through the support programme.

## **AMO GmbH**

Otto-Blumenthal-Str. 25 52074 Aachen Germany

Email: 2D-PL@amo.de

Website: http://www.2DPilotLine.eu