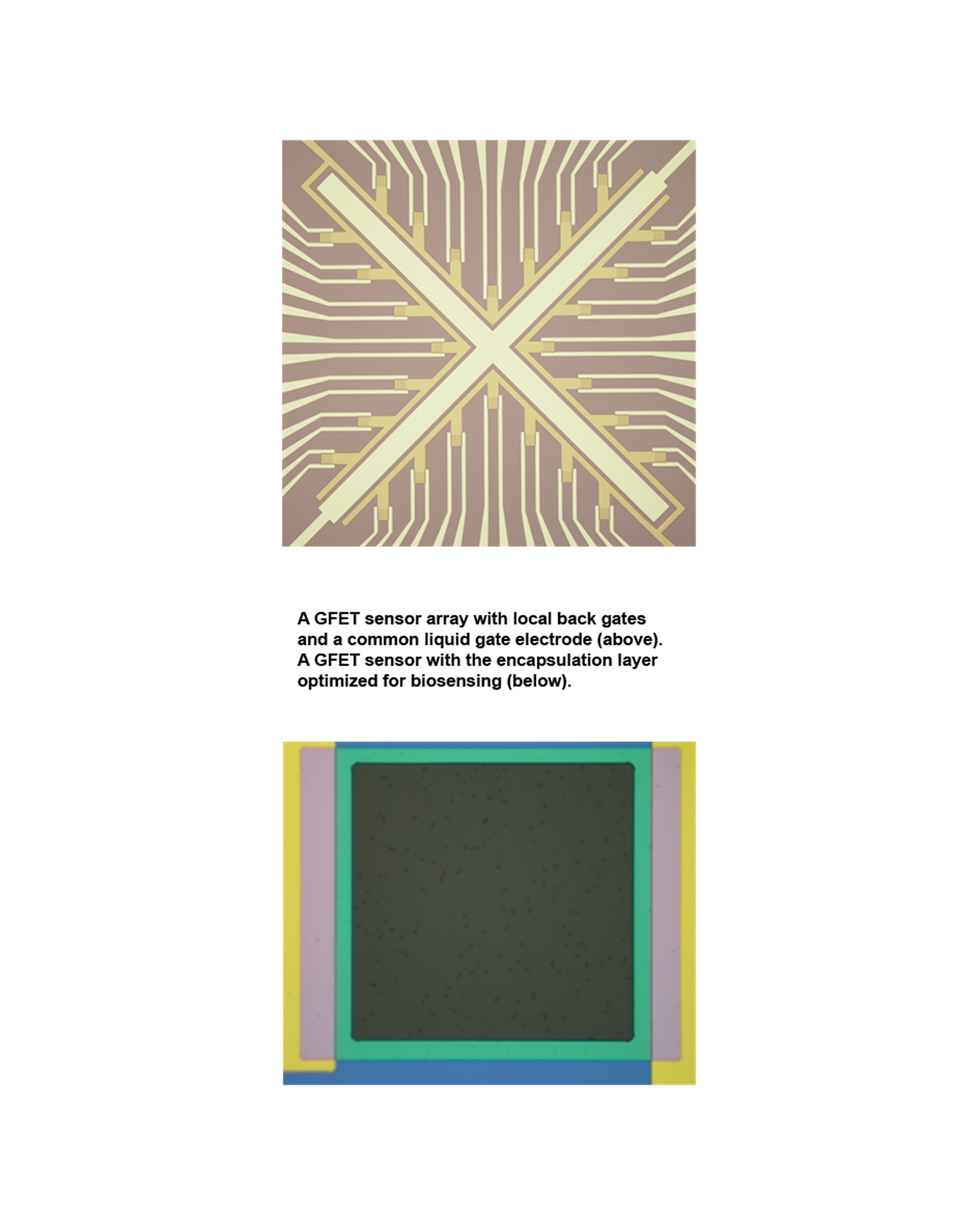

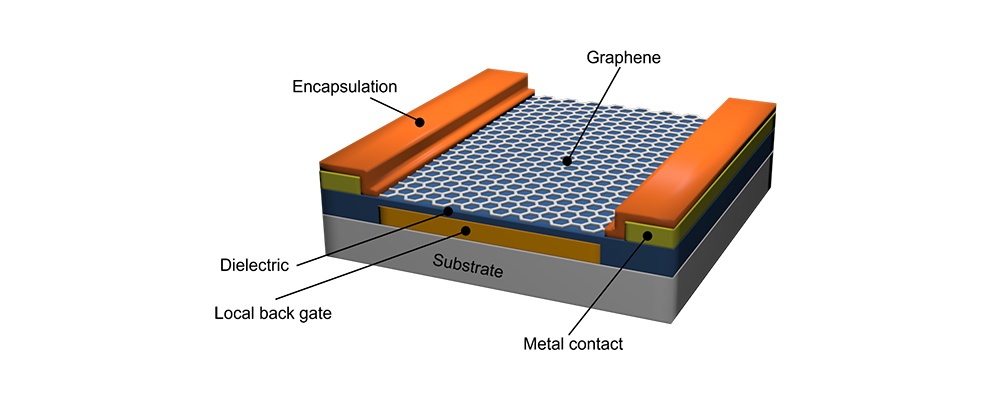

The offered baseline process for the second MPW run is a GFET including a top/bottom contact with an optional local or global back gate, an optional encapsulation and an optional graphene-area opening. The design of the device can be adjusted within the specifications listed below.

Specifications

Substrate

- Silicon/SiO2

- Basic die size : 1 x 1 cm2 (a different size can be consulted upon individual request)

Resolution

- General design rule: 5 µm for in-layer critical dimension and over-layer alignment

Baseline Process

- Gate module

- Contact module

- Graphene module

- Encapsulation module

Characterisation

- Raman characterisation

- Electrical measurements

Application

- Bio/ Gas/ Chemical sensors, Hall Sensors, Photodetectors