Reduced fees

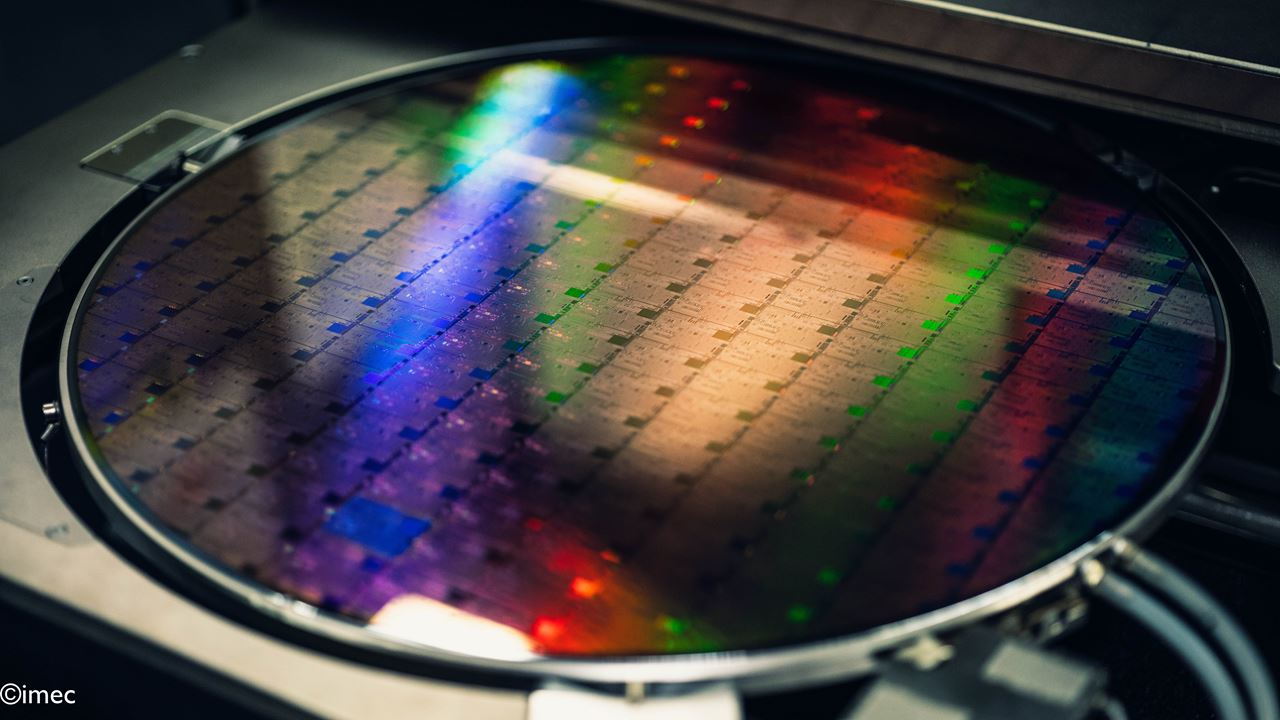

The 2D-PL Support Programme lowers the obstacles for researchers and companies wanting to join our multi-project wafer (MPW) runs. Selected participants can receive a reduction of up to 50% off the MPW fee in exchange for providing feedback on the received devices in the form of a short interview with the hosting pilot line. Your feedback helps us improve future runs.