About VTT

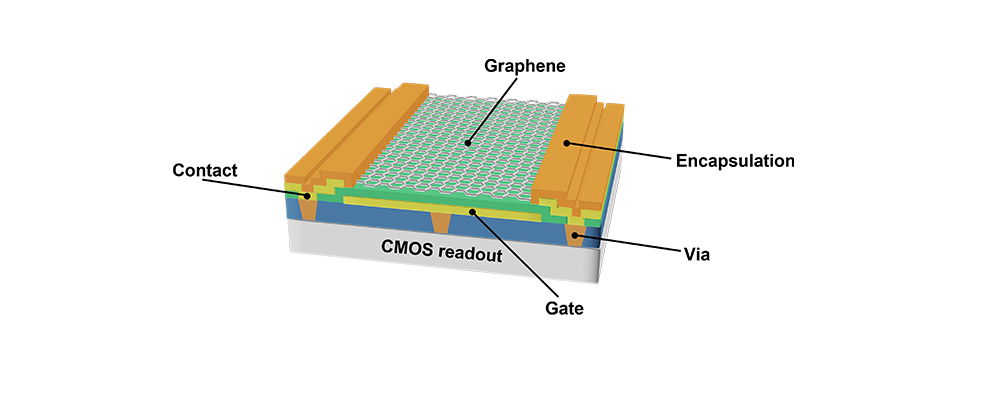

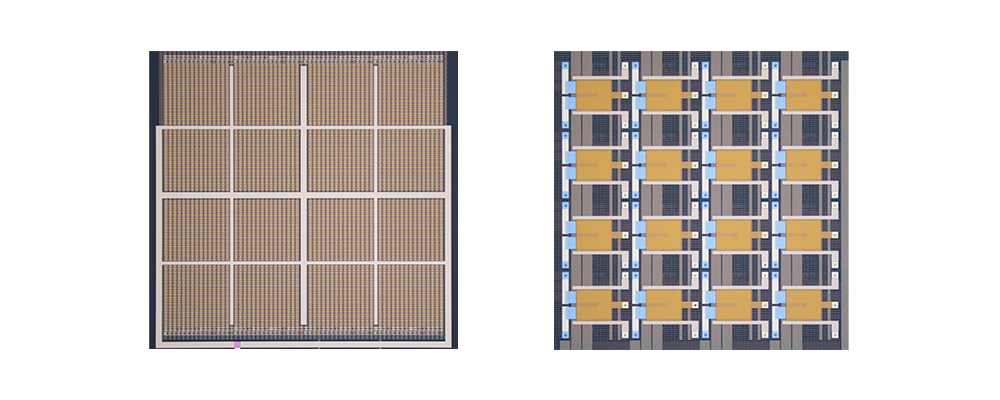

VTT Technical Research Centre of Finland Ltd is a state-owned non-profit research and technology organisation (RTO) with the aim of strengthening Finnish and European industrial competitiveness in multiple fields ranging from sustainable food and energy production to quantum computing. As an RTO VTT acts between universities and industry, bringing basic research towards industrial adaptation and helping the industry in their R&D needs. Graphene industrialisation at VTT is based on 2 600 m2 cleanroom in Micronova, Espoo, with a focus on wafer-scale CVD graphene process optimisation for electronics, photonics and sensors, including the integration on silicon CMOS for multiplexed sensor arrays. In addition to the MPW runs, VTT offers contract research, prototyping and small-scale manufacturing.